Исследование триггеров

Лабораторная работа выполняется с помощью учебного лабораторного стенда LESO2.

1 Цель работы

Целью работы является экспериментальное исследование работы различных типов триггеров.

2 Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений). Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

2.1 RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер.

RS-триггер имеет два логических входа:

- R - установка 0 (от слова reset);

- S - установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q - прямой;

- Q - обратный (инверсный).

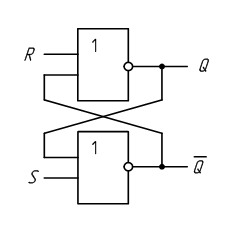

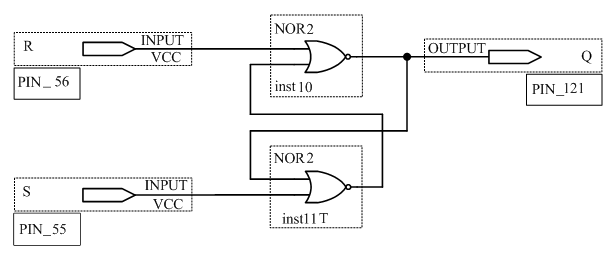

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью (рисунок 2.1).

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль - со входа R, другой - с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента. Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в "0". Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния.

Для описания работы триггера используют таблицу состояний (переходов).

Обозначим:

- Q(t) - состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) - состояние триггера после изменения на входах R и S.

Таблица 2.1 - Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| 0 | 0 | 0 | 0 | Режим хранения информации R=S=0 |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 0 | 1 | Режим установки единицы S=1 |

| 0 | 1 | 1 | 1 | |

| 1 | 0 | 0 | 0 | Режим установки нуля R=1 |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | 0 | * | R=S=1 запрещённая комбинация |

| 1 | 1 | 1 | * |

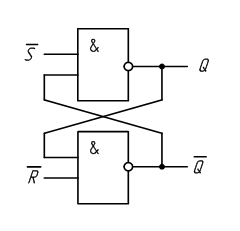

RS-триггер можно построить и на элементах "И-НЕ" (рисунок 2.2).

Входы R и S инверсные (активный уровень "0"). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов "0". Комбинация R=S=0 является запрещённой.

Таблица 2.2 - Таблица переходов RS триггера в базисе "2И-НЕ"

| R | S | Q(t) | Q(t+1) | Пояснения |

| 0 | 0 | 0 | * | R=S=0 запрещённая комбинация |

| 0 | 0 | 1 | * | |

| 0 | 1 | 0 | 0 | Режим установки нуля R=0 |

| 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 1 | Режим установки единицы S=0 |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 0 | Режим хранения информации R=S=1 |

| 1 | 1 | 1 | 1 |

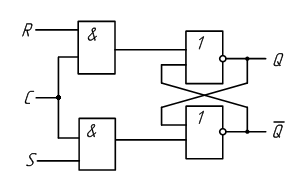

2.2 Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется "опасные гонки"), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена на рисунке 2.3.

Таблица 2.3 - Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 0 | 0 | 1 | 0 | 0 | Режим хранения информации R = S = 0 |

| 0 | 0 | 1 | 1 | 1 | |

| 0 | 1 | 1 | 0 | 1 | Режим установки единицы S =1 |

| 0 | 1 | 1 | 1 | 1 | |

| 1 | 0 | 1 | 0 | 0 | Режим установки нуля R=1 |

| 1 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 1 | 0 | * | R = S = 1 запрещённая комбинация |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

2.3 D - триггер

D-триггер имеет 1 информационный вход (D-вход). Бывают только синхронные D-триггеры. Состояние информационного входа передаётся на выход под действием синхроимпульса (вход С).

Таблица 2.4 - Таблица переходов D-триггера

| C | D | Q(t) | Q(t+1) | Пояснения |

| 0 | * | 0 | 0 | Режим хранения информации |

| 0 | * | 1 | 1 | |

| 1 | 0 | * | 0 | Режим записи информации |

| 1 | 1 | * | 1 |

Если на входе D - "1", то по приходу синхроимпульса Q = 1.

Если на D "0", то Q =0.

2.4 Счётный триггер (Т-триггер)

Т-триггер имеет один счётный информационный вход.Триггер переключается каждый раз в противоположное состояние, когда на вход Т поступает управляющий сигнал.

Таблица 2.5 - Таблица переходов Т триггера

| T | Q(t) | Q(t+1) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

2.5 Универсальный триггер (JK-триггер)

Такой триггер имеет информационные входы J и К, которые по своему влиянию аналогичны входам S и R тактируемого RS-триггера:

- при J=1, K=0 триггер по тактовому импульсу устанавливается в состояние Q=1;

- при J= 0, К=1 - переключается в состояние Q=0;

- при J=K=0 - хранит ранее принятую информацию.

Но в отличие от синхронного RS-триггера одновременное присутствие логических 1 на информационных входах не является для JK-триггера запрещённой комбинацией и приводит триггер в противоположное состояние.

Таблица 2.6 - Таблица переходов JK триггера

| K | J | C | Q(t) | Q(t+1) |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

3 Задание к работе

|

Вопросы |

3.1 Исследовать асинхронный RS- триггер

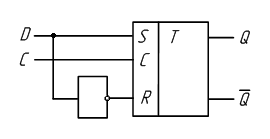

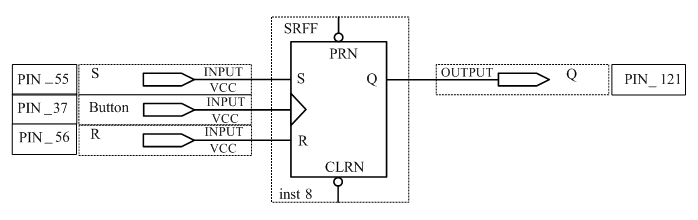

Сконфигурировать ПЛИС в соответствии с рисунком 3.1.

Все используемые элементы располагаются в Symbol tools->Primitives.

Устанавливая с помощью переключателей S7 и S8 различные комбинации логических уровней и наблюдая за светодиодом LED8 заполнить таблицу 3.1

Таблица 3.1 - Таблица переходов для асинхронного RS триггера на элементах "ИЛИ-НЕ"

| R | S | Q(t) | Q(t+1) |

| 0 | 0 | 0 | |

| 0 | 0 | 1 | |

| 0 | 1 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 0 | |

| 1 | 0 | 1 |

3.2 Исследовать синхронный RS триггер

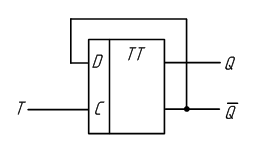

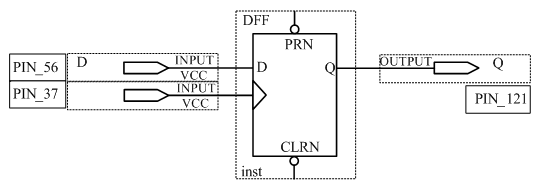

Сконфигурировать ПЛИС в соответствии с рисунком 3.2.

Триггер взять из библиотеки Primitives->Storage. Устанавливая с помощью переключателей S7 и S8 различные комбинации логических уровней и затем нажимая на кнопку Button, заполнить таблицу переходов 3.2.

Таблица 3.2 - Таблица переходов для синхронного RS триггера

| R | S | C | Q(t) | Q(t+1) |

| 0 | 0 | 1 | 0 | |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 1 | 0 | |

| 0 | 1 | 1 | 1 | |

| 1 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 1 | |

| 0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 1 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 0 | 1 |

3.3 Исследовать D-триггер

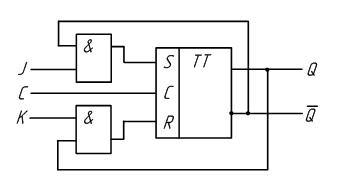

Сконфигурировать ПЛИС в соответствии с рисунком 3.3.

Устанавливая с помощью переключателя S8 различные логические уровни на выходе D и затем нажимая на кнопку Button, заполнить таблицу переходов 3.3.

Таблица 3.3 - Таблица переходов для синхронного D триггера

| D | C | Q(t) | Q(t+1) |

| * | 0 | 0 | |

| * | 0 | 1 | |

| 0 | 1 | 0 | |

| 1 | 1 | 1 |

3.4 Исследовать синхронный T-триггер

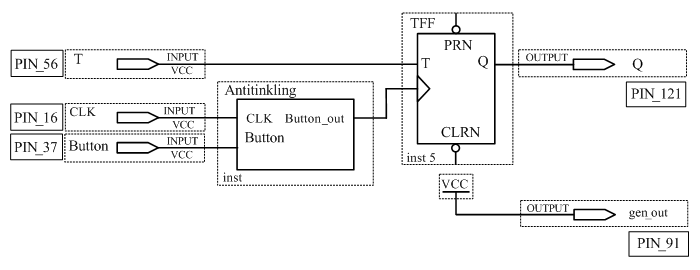

Сконфигурировать ПЛИС в соответствии с рисунком 3.4.

Блок Antitinkling необходим для подавления дребезга кнопки.

ВНИМАНИЕ! Для того, что бы выполнить блок Antitinkling, прочтите инструкцию Борьба с дребезгом контактов.

Вход CLK соединяется с pin16, вход Button соединяется с pin37. Выход Antitinkling соединить с входом синхронизации триггера. Остальные входы соединить согласно рисунку 3.4.

Устанавливая с помощью переключателя S8 различные логические уровни на выходе D и затем, нажимая на кнопку Button, заполнить таблицу переходов 3.4.

Таблица 3.4 - Таблица переходов для синхронного D триггера

| T | C | Q(t) | Q(t+1) |

| 1 | 1 | 0 | |

| 1 | 1 | 1 | |

| 0 | 1 | 0 | |

| 0 | 1 | 1 |

3.5 Исследование синхронного JK триггера

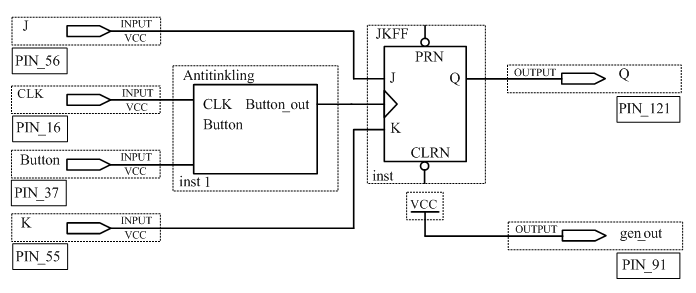

Сконфигурировать ПЛИС в соответствии с рисунком 3.5.

Блок Antitinking подключить так же как, было сделано в предыдущем задании. Устанавливая с помощью переключателя S7 и S8 различные логические уровни на входах J, K и затем, нажимая на кнопку Button, заполнить таблицу переходов 3.5.

Таблица 3.5 - Таблица переходов для JK триггера

| J | K | C | Q(t) | Q(t+1) |

| 0 | 0 | 1 | 0 | |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 1 | 0 | |

| 0 | 1 | 1 | 1 | |

| 1 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 0 | |

| 1 | 1 | 1 | 1 |

4 Содержание отчёта

- Цель работы.

- Схемы исследования триггеров.

- Привести условные графические обозначения исследуемых триггеров.

- Таблица переходов исследуемых триггеров.

- Выводы по каждому заданию.

5 Контрольные вопросы

|

Задание |

- Чем определяется быстродействие триггера?

- Начертить схему RS-триггера на логических элементах "ИЛИ-НЕ" и пояснить принцип его работы.

- Почему JK-триггер называется универсальным?

- Пояснить по таблице переходов работу D-триггера.

- Какой характерной особенностью обладает периодическая последовательность импульсов на входе T-триггера?

- Способы описания последовательных цифровых устройств.

- Каким преимуществом обладает двухступенчатый триггер?